Cray-3 - Cray-3

Le Cray-3 était un supercalculateur vectoriel , le successeur désigné par Seymour Cray du Cray-2 . Le système a été l'une des premières applications majeures des semi-conducteurs à l'arséniure de gallium (GaAs) en informatique, utilisant des centaines de circuits intégrés personnalisés emballés dans un processeur de 1 pied cube (0,028 m 3 ) . L'objectif de conception était une performance d'environ 16 GFLOPS , environ 12 fois celle du Cray-2.

Les travaux ont commencé sur le Cray-3 en 1988 dans les laboratoires de développement de Cray Research (CRI) à Chippewa Falls, Wisconsin . D'autres équipes du laboratoire travaillaient sur des conceptions aux performances similaires. Pour concentrer les équipes, l'effort Cray-3 a été déplacé vers un nouveau laboratoire à Colorado Springs, Colorado plus tard cette année-là. Peu de temps après, le siège social de Minneapolis a décidé de mettre fin aux travaux sur le Cray-3 en faveur d'un autre design, le Cray C90 . En 1989, l'effort de Cray-3 a été transféré à une société nouvellement formée, Cray Computer Corporation (CCC).

Le client de lancement, Lawrence Livermore National Laboratory , a annulé sa commande en 1991 et un certain nombre de dirigeants de l'entreprise sont partis peu de temps après. La première machine était enfin prête en 1993, mais sans client de lancement, elle a plutôt été prêtée comme unité de démonstration au National Center for Atmospheric Research à Boulder . L'entreprise a fait faillite en mai 1995 et la machine a été officiellement mise hors service.

Avec la livraison du premier Cray-3, Seymour Cray est immédiatement passé à la conception similaire mais améliorée du Cray-4 , mais la société a fait faillite avant qu'elle ne soit complètement testée. Le Cray-3 était la dernière conception achevée de Cray; avec la faillite de CCC, il a formé SRC Computers pour se concentrer sur des conceptions parallèles, mais est décédé dans un accident de voiture en 1996 avant que ce travail ne soit livré.

Histoire

Arrière-plan

Seymour Cray a commencé la conception du Cray-3 en 1985, dès que le Cray-2 a atteint la production. Cray s'est généralement fixé pour objectif de produire de nouvelles machines avec des performances dix fois supérieures aux modèles précédents. Bien que les machines n'atteignent pas toujours cet objectif, il s'agissait d'une technique utile pour définir le projet et clarifier le type d'améliorations de processus nécessaires pour y parvenir. Pour le Cray-3, il a décidé de se fixer un objectif d'amélioration des performances encore plus élevé, une augmentation de 12x par rapport au Cray-2.

Cray avait toujours attaqué le problème de l'augmentation de la vitesse avec trois avances simultanées ; plus d' unités d'exécution pour donner au système un parallélisme plus élevé , un conditionnement plus serré pour réduire les retards de signal et des composants plus rapides pour permettre une vitesse d'horloge plus élevée. Des trois, Cray était normalement le moins agressif le dernier; ses conceptions avaient tendance à utiliser des composants qui étaient déjà largement utilisés, par opposition à des conceptions de pointe.

Pour le Cray-2, il a introduit un nouveau système d'emballage 3D pour ses circuits intégrés afin de permettre des densités plus élevées, et il est apparu qu'il y avait une certaine marge d'amélioration dans ce processus. Pour la nouvelle conception, il a déclaré que tous les fils seraient limités à une longueur maximale de 1 pied (0,30 m). Cela exige le processeur soit en mesure de répondre à un 1 pied cube (0,028 m 3 blocs), d' environ 1 / 3 celle de la CPU Cray-2. Cela augmenterait non seulement les performances, mais rendrait le système 27 fois plus petit.

Pour une augmentation des performances de 12x, l'emballage seul ne suffirait pas, les circuits sur les puces elles-mêmes devraient également accélérer. Le Cray-2 semblait repousser les limites de la vitesse des transistors à base de silicium à 4,1 ns (244 MHz), et il ne semblait pas que rien de plus qu'un autre 2x serait possible. Si l'objectif de 12x devait être atteint, des changements plus radicaux seraient nécessaires et une approche « high tech » devrait être utilisée.

Cray avait l'intention d'utiliser des circuits à l' arséniure de gallium dans le Cray-2, qui non seulement offriraient des vitesses de commutation beaucoup plus élevées, mais utiliseraient également moins d'énergie et donc fonctionneraient également plus froid. Au moment de la conception du Cray-2, l'état de la fabrication du GaAs n'était tout simplement pas à la hauteur de la fourniture d'un supercalculateur. Au milieu des années 1980, les choses avaient changé et Cray a décidé que c'était la seule voie à suivre. Compte tenu du manque d'investissement de la part des grands fabricants de puces, Cray a décidé d'investir dans une startup de fabrication de puces GaAs, GigaBit Logic, et de les utiliser comme fournisseur interne.

Décrivant le système en novembre 1988, Cray a déclaré que l'augmentation des performances de 12 fois serait composée d'une augmentation de trois fois due aux circuits GaAs et de quatre fois en raison de l'utilisation de plus de processeurs. L'un des problèmes avec le Cray-2 était les mauvaises performances de multitraitement en raison de la bande passante limitée entre les processeurs, et pour résoudre ce problème, le Cray-3 adopterait l'architecture beaucoup plus rapide utilisée dans le Cray Y-MP . Cela fournirait une performance de conception de 8000 MIPS , ou 16 GFLOPS .

Développement

Le Cray-3 devait initialement être livré en 1991. C'était à une époque où le marché des superordinateurs diminuait rapidement, passant de 50 % de croissance annuelle en 1980 à 10 % en 1988. Dans le même temps, Cray Research travaillait également sur le Y-MP, une version multiprocesseur plus rapide de l'architecture du système retraçant ses ancêtres au Cray-1 d'origine . Afin de concentrer les groupes Y-MP et Cray-3, et avec le soutien personnel de Cray, le projet Cray-3 a déménagé dans un nouveau centre de recherche à Colorado Springs .

En 1989, le Y-MP commençait les livraisons, et le principal laboratoire CRI à Chippewa Falls, Wisconsin , est passé au C90, une nouvelle amélioration de la série Y-MP. Avec seulement 25 Cray-2 vendus, la direction a décidé que le Cray-3 devrait être mis en développement "à faible priorité". En novembre 1988, le laboratoire de Colorado Springs est devenu Cray Computer Corporation (CCC), CRI conservant 10 % des actions de la nouvelle société et fournissant un billet à ordre de 85 millions de dollars pour financer le développement. Cray lui-même n'était pas actionnaire de la nouvelle société et travaillait sous contrat. Comme CRI a conservé le bail du bâtiment d'origine, la nouvelle société a dû déménager à nouveau, ce qui a entraîné de nouveaux retards.

En 1991, le développement était en retard. Le développement s'est encore ralenti lorsque Lawrence Livermore National Laboratory a annulé sa commande pour la première machine, en faveur du C90. Plusieurs cadres, dont le PDG, ont quitté l'entreprise. La société a ensuite annoncé qu'elle recherchait un client ayant besoin d'une version plus petite de la machine, avec quatre à huit processeurs.

Le premier (et unique) modèle de production (numéro de série S5, nommé Graywolf ) a été prêté à NCAR comme système de démonstration en mai 1993. La version de NCAR était configurée avec 4 processeurs et une mémoire commune de 128 MWord (mots de 64 bits, 1 Go) . En service, la RAM statique s'est avérée problématique. Il a également été découvert que le code racine carrée contenait un bogue qui entraînait 1 erreur sur 60 millions de calculs. De plus, l'un des quatre processeurs ne fonctionnait pas de manière fiable.

La CCC a déclaré faillite en mars 1995, après avoir dépensé environ 300 millions de dollars de financement. La machine de NCAR a été officiellement mise hors service le lendemain. Sept armoires système, ou "réservoirs", numéros de série S1 à S7, ont été construites pour les machines Cray-3. La plupart étaient destinés aux petites machines à deux processeurs. Trois des plus petits réservoirs ont été utilisés sur le projet Cray-4 , essentiellement un Cray-3 avec 64 processeurs plus rapides fonctionnant à 1 ns (1 GHz) et emballés dans un espace encore plus petit. Un autre a été utilisé pour le projet Cray-3/SSS .

L'échec du Cray-3 était en grande partie dû à l'évolution du climat politique et technique. La machine a été conçue pendant l'effondrement du Pacte de Varsovie et la fin de la guerre froide , ce qui a entraîné une réduction massive des achats de supercalculateurs. Parallèlement, le marché investit de plus en plus dans des conceptions massivement parallèles (MP ou MPP). Cray a critiqué cette approche et a été cité par le Wall Street Journal comme disant que les systèmes MPP n'avaient pas encore prouvé leur suprématie sur les ordinateurs vectoriels, notant la difficulté de nombreux utilisateurs à programmer pour de grandes machines parallèles. "Je ne pense pas qu'ils auront jamais un succès universel, du moins pas de mon vivant".

Architecture

Conception logique

L'architecture du système Cray-3 comprenait un système de traitement de premier plan , jusqu'à 16 processeurs d'arrière-plan et jusqu'à 2 gigawords (16 Go) de mémoire commune . Le système de premier plan était dédié aux entrées/sorties et à la gestion du système. Il comprenait un processeur 32 bits et quatre canaux de données synchrones pour le stockage de masse et les périphériques réseau, principalement via les canaux HiPPI .

Chaque processeur d'arrière-plan se composait d'une section de calcul , d'une section de contrôle et d' une mémoire locale . La section de calcul a effectué une arithmétique scalaire, à virgule flottante et vectorielle 64 bits . La section de contrôle a fourni des tampons d'instructions, des fonctions de gestion de mémoire et une horloge en temps réel . 16 kmots (128 koctets) de mémoire locale à grande vitesse ont été incorporés dans chaque processeur d'arrière-plan pour être utilisés comme mémoire de travail temporaire.

La mémoire commune était constituée de silicium CMOS SRAM , organisé en octants de 64 banques chacun, avec jusqu'à huit octants possibles. La taille du mot était de 64 bits plus huit bits de correction d'erreur , et la bande passante totale de la mémoire était évaluée à 128 gigaoctets par seconde.

Conception du processeur

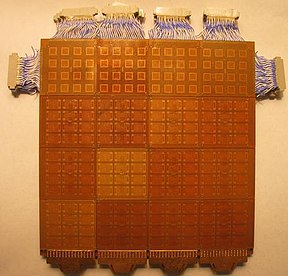

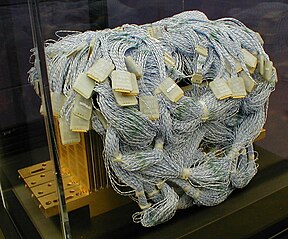

Comme pour les conceptions précédentes, le cœur du Cray-3 se composait d'un certain nombre de modules , chacun contenant plusieurs cartes de circuits imprimés remplies de pièces. Afin d'augmenter la densité, les puces GaAs individuelles n'ont pas été emballées et plusieurs ont été montées directement avec une liaison or par ultrasons sur une carte d'environ 1 pouce (25 mm) de côté. Les cartes ont ensuite été retournées et couplées à une deuxième carte portant le câblage électrique, les fils de cette carte passant à travers des trous jusqu'au côté "inférieur" (opposé aux puces) du support de puce où ils étaient collés, prenant ainsi en sandwich la puce entre les deux couches de planche. Ces sous - modules ont ensuite été empilés à quatre profondeurs et, comme dans le Cray-2, câblés les uns aux autres pour former un circuit 3D.

Contrairement au Cray-2, les modules Cray-3 comprenaient également des connecteurs de bord . Seize de ces sous-modules ont été connectés ensemble dans un réseau 4 × 4 pour former un seul module mesurant 121 par 107 par 7 millimètres (4,76 pouces × 4,21 pouces × 0,28 pouces). Même avec cet emballage avancé, la densité du circuit était faible même par rapport aux normes des années 1990, à environ 96 000 portes par pouce cube. Les processeurs modernes offrent des nombres de portes de millions par pouce carré, et le passage aux circuits 3D n'était encore qu'à l'étude à partir de 2017.

Trente-deux de ces modules ont ensuite été empilés et câblés avec une masse de fils à paires torsadées dans un seul processeur. Le temps de cycle de base était de 2,11 ns, soit 474 MHz, permettant à chaque processeur d'atteindre environ 0,948 GFLOPS , et une machine à 16 processeurs un théorique 15,17 GFLOP. La clé de la haute performance était l'accès à haute vitesse à la mémoire principale, qui a permis à chaque processus d'exploser jusqu'à 8 Go/s.

Design mécanique

Les modules étaient maintenus ensemble dans un châssis en aluminium appelé « brique ». Les briques ont été immergées dans du fluorinert liquide pour le refroidissement, comme dans le Cray-2. Un système à quatre processeurs avec 64 modules de mémoire a dissipé environ 88 kW de puissance. L'ensemble du système à quatre processeurs mesurait environ 20 pouces (510 mm) de haut et d'avant en arrière, et un peu plus de 2 pieds (0,61 m) de large.

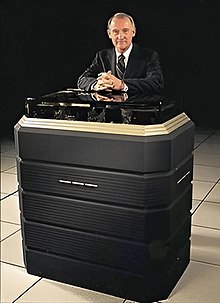

Pour les systèmes avec jusqu'à quatre processeurs, l'assemblage du processeur était placé sous un couvercle en acrylique bronzé translucide au sommet d'une armoire de 42 pouces (1,1 m) de large, 28 pouces (0,71 m) de profondeur et 50 pouces (1,3 m) de haut, avec le la mémoire en dessous, puis les alimentations et les systèmes de refroidissement en bas. Le système à huit et 16 processeurs aurait été logé dans une armoire octogonale plus grande. Dans l'ensemble, le Cray-3 était considérablement plus petit que le Cray-2, lui-même relativement petit par rapport aux autres supercalculateurs.

En plus de l'armoire système, un système Cray-3 avait également besoin d'un ou deux (selon le nombre de processeurs) boîtiers de contrôle système (ou "C-Pods"), 52,5 pouces (1,33 m) carrés et 55,3 pouces (1,40 m) élevé, contenant des équipements de contrôle d'alimentation et de refroidissement.

Configurations du système

Les configurations possibles du Cray-3 suivantes ont été officiellement spécifiées :

| Nom | Processeurs | Mémoire (Mmots) | Modules d'E/S |

|---|---|---|---|

| Cray-3/1-256 | 1 | 256 | 1 |

| Cray-3/2-256 | 2 | 256 | 1 |

| Cray-3/4-512 | 4 | 512 | 3 |

| Cray-3/4-1024 | 4 | 1024 | 3 |

| Cray-3/4-2048 | 4 | 2048 | 3 |

| Cray-3/8-1024 | 8 | 1024 | 7 |

| Cray-3/8-2048 | 8 | 2048 | 7 |

| Cray-16-3-2048 | 16 | 2048 | 15 |

Logiciel

Le Cray-3 exécutait le système d'exploitation Colorado Springs ( CSOS ) qui était basé sur le système d' exploitation UNICOS version 5.0 de Cray Research . Une différence majeure entre CSOS et UNICOS était que CSOS a été porté au standard C avec toutes les extensions PCC qui ont été utilisées dans UNICOS supprimées.

La plupart des logiciels disponibles sous le Cray-3 étaient dérivés de Cray Research et comprenaient par exemple le système X Window , vectorisant les compilateurs FORTRAN et C , NFS et une pile TCP/IP .

Les références

Citations

Bibliographie

- Systèmes de superordinateurs CRAY-3 (PDF) (brochure). Cray Computer Corporation. 1993.

- Hill et autres, Mark Donald (2000). Lectures en architecture informatique . Éditions professionnelles du Golfe. ISBN 9781558605398.

- Lester, Lynda (juin 1993). "La fabrication d'un CRAY-3" . Neuvième conférence des utilisateurs SCD . Archivé de l'original le 30 juin 2007.

- MacKenzie, Donald (1998). Connaître les machines : essais sur le changement technique . Presse MIT. ISBN 9780262631884.

- Murray, Charles (1997). Les Supermen : l'histoire de Seymour Cray et des sorciers techniques derrière le supercalculateur . John Wiley.

- Trew, Arthur (2012). « Supercalculateurs vectoriels : il n'est jamais trop tard pour paralléliser » . Dans Trew, Arthur ; Wilson, Greg (éd.). Passé, présent, parallèle : une enquête sur les systèmes informatiques parallèles disponibles . Springer Science et affaires. p. 245. ISBN 9781447118428.