DÉC J-11 - DEC J-11

Le J-11 est un jeu de puces à microprocesseur qui implémente l' architecture de jeu d'instructions PDP-11 (ISA) développée conjointement par Digital Equipment Corporation et Harris Semiconductor . Il s'agissait d'un jeu de puces haut de gamme conçu pour intégrer les performances et les fonctionnalités du PDP-11/70 sur une poignée de puces. Il a été utilisé dans les PDP-11/73 , PDP-11/83 et Professional 380 .

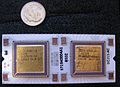

Il se composait d'une puce de chemin de données et d'une puce de contrôle dans des boîtiers sans fil en céramique montés sur un seul boîtier DIP hybride en céramique. La puce de contrôle incorporait un séquenceur de contrôle et une ROM à microcode. Une puce d'accélérateur à virgule flottante (FPA) séparée en option pouvait être utilisée et était emballée dans un DIP standard. La puce de chemin de données et la puce de contrôle ont été fabriquées par Harris dans un processus CMOS tandis que le FPA a été fabriqué par Digital dans leur processus NMOS " ZMOS ".

La conception à l'origine était destinée à prendre en charge plusieurs puces de contrôle pour permettre la mise en œuvre d'instructions supplémentaires telles que le jeu d'instructions commerciales (CIS), mais aucune puce de contrôle n'a jamais été proposée.

Un clone du J-11 a été fabriqué en Union soviétique sous la désignation KN1831VM1 ( russe : КН1831ВМ1 ).