Intel 4004 - Intel 4004

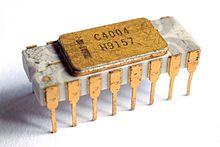

Microprocesseur Intel C4004 en céramique blanche avec traces grises

| |

| informations générales | |

|---|---|

| Lancé | 15 novembre 1971 |

| Abandonné | 1981 |

| Fabricant(s) commun(s) | |

| Performance | |

| Max. Fréquence d'horloge du processeur | 740-750 kHz |

| Largeur des données | 4 bits |

| Largeur de l'adresse | 12 bits (multiplexé) |

| Architecture et classement | |

| Application | Calculatrice Busicom, manipulation arithmétique |

| Min. taille de la caractéristique | 10 m |

| Jeu d'instructions | Orienté BCD 4 bits |

| Spécifications physiques | |

| Transistors | |

| Paquets) | |

| Prise(s) | |

| Histoire | |

| Successeur | Intel 4040 |

L' Intel 4004 est une unité centrale de traitement (CPU) 4 bits publiée par Intel Corporation en 1971. C'était le premier microprocesseur produit commercialement et le premier d'une longue lignée de processeurs Intel .

La conception de la puce, mise en œuvre avec la technologie de porte en silicium MOS, a commencé en avril 1970 et a été créée par Federico Faggin qui a dirigé le projet du début à la fin en 1971. Marcian Hoff a formulé et dirigé la proposition architecturale en 1969, et Masatoshi Shima a contribué à l'architecture et plus tard à la conception logique. La première livraison d'un 4004 pleinement opérationnel a eu lieu en mars 1971 à Busicom Corp. du Japon pour son prototype d'ingénierie de calculatrice d'impression 141-PF (maintenant exposé au Computer History Museum de Mountain View, en Californie). Cette calculatrice pour laquelle la 4004 a été conçue et construite à l'origine comme une puce personnalisée a été commercialisée pour la première fois en juillet 1971.

Federico Faggin a accompli ce que personne n'avait réalisé auparavant : intégrer un processeur à usage général dans une petite puce de silicium commerciale. Il a inventé comment concevoir et mettre en place 2 300 transistors à logique aléatoire en une seule puce avec une vitesse 5 fois supérieure et deux fois la densité de circuit (la moitié du coût) de la technologie de grille métallique en place. Cette intégration sans précédent a été réalisée grâce à la nouvelle technologie de processus qu'il a inventée chez Fairchild Semiconductors en 1968, la technologie de grille en silicium MOS (SGT), avec laquelle il a également conçu le premier circuit intégré commercial (le Fairchild 3708). Pour concevoir l'Intel 4004, Faggin a utilisé le SGT avec deux de ses nouvelles inventions, le "contact enterré" et la "charge d'amorçage dans une porte en silicium", qui ont permis la vitesse, la puissance et le coût nécessaires pour un microprocesseur polyvalent utile. .

Le 4004 a été le premier circuit logique aléatoire intégré dans une puce utilisant la technologie de grille de silicium (SGT) MOS (métal-oxyde-semiconducteur ). Il s'agissait de la conception de circuits intégrés (CI) la plus avancée entreprise jusqu'alors. Hoff, chef du département de recherche d'applications d'Intel, avait formulé une proposition architecturale consistant en une architecture en blocs avec un jeu d'instructions en 1969, en discutant avec des ingénieurs de Busicom dirigés par Shima et avec l'aide de Stan Mazor. Hoff et Mazor n'étaient pas des concepteurs de puces MOS et n'ont pas participé à la conception ou au développement du 4004.

La conception de la puce a été réalisée indépendamment dans le département MOS, différent de la recherche d'application. Il ne pouvait être réalisé que par un concepteur ayant une connaissance approfondie de la technologie des procédés MOS et du nouveau SGT. Faggin a été embauché chez Intel en avril 1970 par Fairchild Semiconductor pour être le chef de projet et le concepteur du 4004 et il est passé à la fabrication d'une puce entièrement fonctionnelle en mars 1971. Faggin a apporté à Intel sa maîtrise du SGT qu'il avait inventé chez Fairchild ( en 1968) et l'a utilisé pour développer sa nouvelle méthodologie de conception de puces aléatoires qui a été la clé de la fabrication du premier et de tous les premiers microprocesseurs Intel. Shima, représentant Busicom, a été engagé avec Hoff et Mazor dans la phase architecturale en 1969 et il a également aidé Faggin avec la conception logique finale pendant 6 mois en 1970.

En novembre 1971, avec l'annonce prophétique "Annoncer une nouvelle ère dans l'électronique intégrée", le 4004 a été commercialisé sur le marché général. Le 4004 était le premier processeur monolithique, entièrement intégré dans une petite puce. Un tel exploit d'intégration a été rendu possible par l'utilisation de la nouvelle technologie de grille de silicium pour les circuits intégrés, développée à l'origine par Faggin (avec Tom Klein) chez Fairchild Semiconductor en 1968, qui a permis deux fois le nombre de transistors à logique aléatoire et une augmentation de vitesse d'un facteur cinq par rapport à la technologie de grille en aluminium MOS en place. Faggin a également inventé la charge bootstrap avec grille en silicium et le "contact enterré", améliorant la vitesse et la densité du circuit par rapport à la grille en aluminium.

Le microprocesseur 4004, la ROM 4001, la RAM 4002 et le registre à décalage 4003 constituaient les quatre puces du jeu de puces Intel MCS-4 . Avec ces composants, de petits ordinateurs avec des quantités variables de mémoire et d'installations d'E/S pourraient être construits.

Puces CPU contemporaines

Trois autres conceptions de puces CPU ont été produites à peu près au même moment : les systèmes à quatre phases AL1, réalisés en 1969 ; le MP944 , achevé en 1970 et utilisé dans l'avion de chasse F-14 Tomcat ; et la puce Texas Instruments TMS-0100, annoncée le 17 septembre 1971. La MP944 était un ensemble de six puces formant un seul processeur. La puce TMS0100 a été présentée comme une "calculatrice sur puce" avec la désignation originale TMS1802NC. Cette puce contient un processeur très primitif et ne peut être utilisée que pour implémenter diverses calculatrices simples à quatre fonctions. C'est le précurseur du TMS1000 , introduit en 1974, qui est considéré comme le premier microcontrôleur, c'est-à-dire un ordinateur sur une puce contenant non seulement le CPU, mais aussi les fonctions ROM, RAM et E/S. La famille MCS-4 de quatre puces développée par Intel, dont le 4004 est le processeur ou le microprocesseur, était beaucoup plus polyvalente et puissante que le TMS1000 à puce unique, permettant la création d'une variété de petits ordinateurs pour diverses applications.

Zilog , la première société entièrement dédiée aux microprocesseurs et microcontrôleurs, a été créée par Federico Faggin et Ralph Ungermann fin 1974.

Histoire et fabrication

La première mention publique de 4004 était une publicité dans l'édition du 15 novembre 1971 d' Electronic News . La première livraison était à Busicom pour leur calculateur prototype d'ingénierie en mars 1971, suivi de leur calculateur prototype 141-PF disponible dans le commerce sur le marché en juillet 1971. Emballé dans un boîtier double en ligne en céramique à 16 broches , le 4004 a été le premier processeur d'ordinateur disponible dans le commerce conçu et fabriqué par puce fabricant Intel , qui avait précédemment fait semiconducteur puces de mémoire. Les principaux concepteurs de la puce étaient Federico Faggin , le chef du projet après la finalisation de la définition architecturale avec Busicom, qui a créé la méthodologie de conception et la conception de la puce à base de silicium ; Ted Hoff qui a formulé l'architecture, à la fois d'Intel, et Masatoshi Shima de Busicom qui a aidé au développement.

Faggin, le seul concepteur de puces parmi les ingénieurs du projet MCS-4, était le seul à avoir de l'expérience dans la logique aléatoire et la conception de circuits à semi-conducteur à oxyde métallique (MOS) . Il possédait également une connaissance cruciale de la nouvelle technologie de processus de grille en silicium avec grilles auto-alignées , qu'il avait créée chez Fairchild en 1968. Chez Fairchild en 1968, Faggin a également conçu et fabriqué le premier circuit intégré commercial au monde utilisant SGT, le Fairchild 3708 qui a été présenté sur la couverture de Electronics (29 septembre 1969). Dès qu'il a rejoint le département Intel MOS, il a créé une nouvelle méthodologie de conception à logique aléatoire basée sur une porte en silicium et a contribué à de nombreuses inventions de technologie et de conception de circuits qui ont permis à leur microprocesseur à puce unique de devenir une réalité. Sa méthodologie a défini le style de conception de tous les premiers microprocesseurs Intel et plus tard du Zilog Z80 . Il a également dirigé le projet MCS-4 et était responsable de son succès (1970-1971). Marcian "Ted" Hoff , chef du département de recherche applicative, a contribué à la proposition architecturale de Busicom en collaboration avec Stanley Mazor en 1969, puis il est passé à d'autres projets. Lorsqu'on lui a demandé d'où il avait trouvé les idées pour l'architecture du premier microprocesseur, Hoff a raconté que Plessey , "une entreprise de tracteurs britannique", avait fait don d'un mini-ordinateur à Stanford , et qu'il avait "joué avec lui un peu" pendant qu'il était là-bas. Shima a conçu le micrologiciel de la calculatrice Busicom et assisté Faggin pendant les six premiers mois de la mise en œuvre. Le directeur du département de conception MOS d'Intel était Leslie L. Vadász . Au moment du développement du MCS-4, l'attention de Vadasz était entièrement concentrée sur l'activité principale des mémoires à semi-conducteurs et il a laissé la direction et la gestion du projet MCS-4 à Faggin.

Busicom avait conçu leur propre usage de spécial LSI chipset pour une utilisation dans leur Busicom 141-PF calculatrice avec imprimante intégrée. Ils ont basé leur conception sur l'architecture de l' Olivetti Programma 101 , l'une des premières calculatrices programmables de table au monde , qu'Olivetti a introduite en 1965. Busicom a chargé Intel de développer leur conception pour la production. Comme l'Olivetti Programma 101, la conception Busicom utilisait une mémoire série lecture-écriture. La mémoire Busicom était basée sur des registres à décalage MOS plutôt que sur la coûteuse mémoire Olivetti basée sur un fil de magnétostriction.

Intel a déterminé que la conception de Busicom était trop complexe, car les mémoires série nécessitaient plus de composants et utiliseraient 40 broches, une norme d'emballage différente de la norme à 16 broches d'Intel. Intel a proposé de développer une nouvelle conception qui pourrait être produite avec un boîtier DIP standard à 16 broches et aurait un jeu d'instructions réduit. La simplification de la mémoire proviendrait de l'utilisation de la mémoire RAM dynamique nouvellement développée par Intel. Cette nouvelle conception était la puce 4004, qui fait partie d'un ensemble de quatre puces, ainsi que des puces de registre à décalage série-à-parallèle ROM , DRAM . Le 4004 a ensuite été conçu par Federico Faggin en utilisant la technologie de grille en silicium et construit avec environ 2 300 transistors et a été suivi l'année suivante par le tout premier microprocesseur 8 bits , le 3 500 transistor 8008 (et le 4040 , un 4004 révisé et amélioré). Ce n'est qu'avec le développement du 8080 40 broches en 1974, un projet conçu et dirigé par Faggin, que les bus d'adresse et de données seront séparés, donnant un accès plus rapide et plus simple à la mémoire.

Le 4004 utilise une technologie pMOS de charge d'amélioration de grille de silicium de processus de 10 m sur une puce de 12 mm 2 et peut exécuter environ 92 000 instructions par seconde ; un seul cycle d'instruction est de 10,8 microsecondes . L' objectif de conception de la fréquence d'horloge d' origine était de 1 MHz, le même que celui de l' IBM 1620 Model I .

L'Intel 4004 a été conçu en découpant physiquement des feuilles de Rubylith en fines bandes pour disposer les circuits à imprimer, un processus rendu obsolète par les capacités actuelles de conception graphique par ordinateur.

Dans le but de tester les puces produites, Faggin a développé un testeur pour les plaquettes de silicium de la famille MCS-4 qui était lui-même piloté par la puce 4004. Le testeur a également servi de preuve pour la direction que le microprocesseur Intel 4004 pouvait être utilisé non seulement dans des produits de type calculatrice, mais aussi pour des applications de contrôle.

Nom et variantes

Lorsque Faggin a conçu la famille MCS-4, il a également baptisé les puces avec des noms distincts : 4001, 4002, 4003 et 4004, rompant avec le schéma de numérotation utilisé par Intel à l'époque qui aurait nécessité les noms 1302, 1105, 1507 , et 1202 respectivement. S'il avait suivi la séquence numérique d'Intel, l'idée que les puces faisaient partie d'une famille de composants destinés à fonctionner ensemble de manière transparente aurait été perdue. Le premier schéma de numérotation d'Intel pour les circuits intégrés utilisait un numéro à quatre chiffres pour chaque composant. Le premier chiffre indiquait la technologie de processus utilisée, le deuxième chiffre indiquait la fonction générique et les deux derniers chiffres du numéro étaient utilisés pour indiquer le numéro séquentiel dans le développement du composant. Le microprocesseur 8008 s'appelait à l'origine 1201, selon les conventions de nommage d'Intel. Avant son introduction sur le marché, le 1201 a été renommé 8008, suite à la nouvelle convention de nommage commencée avec le 4001/4002/4003/4004.

Tadashi Sasaki attribue l'invention de base consistant à diviser la calculatrice en quatre parties avec ROM (4001), RAM (4002), registres à décalage (4003) et CPU (4004) à une femme anonyme du Nara Women's College présente à une réunion de remue-méninges qui a été tenue au Japon avant sa première rencontre avec Robert Noyce d'Intel, menant à l'accord Busicom.

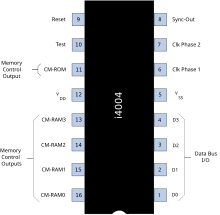

Le 4004 fait partie de la famille MCS-4 de puces LSI qui peuvent être utilisées pour construire des ordinateurs numériques avec différentes quantités de mémoire. Les autres membres de la famille MCS-4 sont des mémoires et des circuits d'entrée/sortie, qui sont nécessaires pour mettre en œuvre un ordinateur complet. Le 4001 est une ROM (mémoire morte) avec quatre lignes de sortie ; le 4002 est une RAM (mémoire à accès aléatoire) avec quatre lignes d'entrée/sortie. Le 4003 est un registre à décalage statique à utiliser pour étendre les lignes d'E/S ; par exemple, pour numériser le clavier ou contrôler une imprimante.

Le 4004 comprend des fonctions de contrôle direct de bas niveau de la sélection des puces mémoire et des E/S, qui ne sont normalement pas gérées par le microprocesseur ; cependant, sa fonctionnalité est limitée en ce qu'il ne peut pas exécuter de code à partir de la RAM et est limité aux instructions fournies dans la ROM (ou à une RAM chargée indépendamment fonctionnant comme ROM - dans les deux cas, le processeur est lui-même incapable d'écrire ou de transférer des données dans un espace mémoire exécutable). Les parties RAM et ROM étaient également inhabituelles dans leur intégration de ports de sortie (et, dans les ROM, d'entrée) qui réduisaient considérablement le nombre minimum de pièces dans un système MCS-4, mais nécessitaient l'inclusion d'une certaine quantité de logique de type processeur sur les puces elles-mêmes pour accepter, décoder et exécuter des instructions de transfert de données de niveau relativement élevé.

L'arrangement standard pour un système 4004 est n'importe quoi jusqu'à 16 × 4001 puces ROM (dans une seule banque) et 16 × 4002 puces RAM (dans quatre banques de quatre), qui fournissent ensemble le stockage de programme de 4 Ko, 1024 + 256 nibbles de données /stockage d'état, plus 64 sorties et 64 entrées/sorties de données externes/lignes de contrôle (qui peuvent elles-mêmes être utilisées pour faire fonctionner, par exemple un 4003). La documentation MCS-4 d'Intel, cependant, affirme que jusqu'à 48 puces ROM et RAM (fournissant jusqu'à 192 lignes de contrôle externes) "dans n'importe quelle combinaison" peuvent être connectées au 4004 "avec du matériel de déclenchement simple", mais refuse de donner d'autres des détails ou des exemples de la façon dont cela serait réellement réalisé.

Spécifications techniques

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

- La fréquence d'horloge maximale est de 740 kHz . Le 4004 avait cette fréquence d'horloge maximale lors de sa sortie initiale en 1971

- Temps de cycle d'instruction : minimum 10,8 s (8 cycles d'horloge / cycle machine)

- Temps d'exécution des instructions 1 ou 2 cycles machine (10,8 ou 21,6 s), 46250 à 92500 instructions par seconde.

- L'ajout de deux nombres à 8 chiffres (32 bits chacun, en supposant des chiffres BCD de 4 bits) prend 850 s revendiqués, soit environ 79 cycles machine (632 ticks d'horloge), pour une moyenne d'un peu moins de 10 cycles (80 ticks) par paire de chiffres et une vitesse de fonctionnement de 1176 × ajouts à 8 chiffres par seconde

- Programme et stockage de données séparés. Contrairement aux conceptions d' architecture de Harvard , cependant, qui utilisent des bus séparés , le 4004, avec son besoin de réduire le nombre de broches, utilise un seul bus multiplexé à 4 bits pour le transfert :

- adresses 12 bits

- instructions 8 bits

- Mots de données de 4 bits

- Capable d'adresser directement 5120 bits (équivalent à 640 octets) de RAM, stockés sous forme de 1280 "caractères" de 4 bits et organisés en groupes représentant 1024 "données" et 256 caractères "état" (512 et 128 octets).

- Capable d'adresser directement 32 768 bits de ROM, équivalents et organisés en 4096 mots de 8 bits (c'est-à-dire octets).

- Le jeu d'instructions contenait 46 instructions (dont 41 avaient une largeur de 8 bits et 5 avaient une largeur de 16 bits)

- Le jeu de registres contient 16 registres de 4 bits chacun

- Pile de sous-programmes interne , 3 niveaux de profondeur.

Niveaux logiques

| symbole | Min | Max | Unité |

|---|---|---|---|

| V SS - DD | +15-5% | +15+5% | V |

| V IL | V DD | V SS -5,5 | V |

| V IH | V SS -1,5 | V SS +0,3 | V |

| V OL | V SS −12 | V SS -6,5 | V |

| V OH | V SS -0,5 | V SS | V |

Puces de soutien

- 4001 : ROM 256 octets (256 instructions de programme 8 bits ) et un port E/S 4 bits intégré. Une puce ROM + E/S 4001 ne peut pas être utilisée dans un système avec une paire 4008/4009.

- 4002 : RAM de 40 octets (80 mots de données de 4 bits ) et un port de sortie de 4 bits intégré ; la partie RAM de la puce est organisée en quatre "registres" de 20 mots de 4 bits :

- 16 mots de données (utilisés pour les chiffres de la mantisse dans la conception originale de la calculatrice), accessibles de manière relativement standard, et

- 4 mots d'état (utilisés pour les chiffres et les signes des exposants dans la conception originale de la calculatrice), accessibles à l'aide de commandes de type E/S à la place du canal d'entrée de la ROM

- 4003 : registre à décalage de sortie parallèle 10 bits pour la numérisation de claviers, d'écrans, d'imprimantes, etc.

- 4008 : verrou d'adresse 8 bits pour l'accès aux puces de mémoire standard et un port de sélection et d'E/S de puce 4 bits intégré

- 4009 : programme et convertisseur d'accès E/S vers mémoire standard et puces E/S

- 4269 : interface clavier/écran

- 4289 : interface mémoire (fonctions combinées des 4008 et 4009)

La spécification minimale du système décrite par Intel consiste en un 4004 avec une seule ROM de programme 4001 de 256 octets ; il n'y a pas besoin explicite de RAM séparée dans les applications de complexité minimale grâce au grand nombre de registres d'index intégrés du 4004, qui représentent l'équivalent de 16 × 4 bits ou 8 × 8 bits (ou un mélange) de RAM de travail, ni pour des puces d'interface simples grâce aux lignes d'E/S intégrées de la ROM. Cependant, à mesure que la complexité du projet augmente, les diverses autres puces de support commencent à devenir utiles.

Emballage

De nombreuses versions de la gamme de processeurs Intel MCS-4 ont été produites. Les premières versions, marquées C (comme C4004), étaient en céramique et utilisaient un motif zébré blanc et gris au dos des puces, souvent appelé « traces grises ». La génération suivante de puces était en céramique blanche unie (également marquée C), puis en céramique gris foncé (D). La plupart des versions les plus récentes de la famille MCS-4 ont également été produites avec du plastique (P).

Utilisation

Le premier produit commercial à utiliser un microprocesseur était le calculateur Busicom 141-PF. Le 4004 a également été utilisé dans le premier jeu de flipper contrôlé par microprocesseur , un prototype produit par Dave Nutting Associates pour Bally en 1974.

Selon Nick Tredennick , concepteur de microprocesseurs et témoin expert dans l'affaire du brevet Boone/Hyatt :

Voici mes opinions à partir de [l'] étude [que j'ai menée pour l'affaire du brevet]. Le premier microprocesseur dans un produit commercial était le Four Phase Systems AL1 . Le premier microprocesseur disponible dans le commerce (vendu en tant que composant) était le 4004 d'Intel.

Un mythe populaire veut que Pioneer 10 , le premier vaisseau spatial à quitter le système solaire, utilisait un microprocesseur Intel 4004. Selon le Dr Larry Lasher du Centre de recherche Ames , l'équipe Pioneer a évalué le 4004, mais a décidé qu'il était trop nouveau à l'époque pour l'inclure dans l'un des projets Pioneer. Le mythe a été répété par Federico Faggin lui-même dans une conférence pour le Computer History Museum en 2006.

Héritage et valeur

Federico Faggin a signé le 4004 avec ses initiales parce qu'il savait que sa conception de porte en silicium incarnait "l'essence du microprocesseur". Un coin du dé indique "FF"

Le 15 novembre 2006, le 35e anniversaire du 4004, Intel a célébré en publiant les schémas de la puce , les masques et le manuel d'utilisation . Une réplique entièrement fonctionnelle de 41 × 58 cm et à l'échelle 130 × de l'Intel 4004 a été construite à l'aide de transistors discrets et exposée en 2006 au Intel Museum de Santa Clara , en Californie.

Le 15 octobre 2010, Faggin, Hoff et Mazor ont reçu la Médaille nationale de la technologie et de l'innovation du président Barack Obama pour leur travail de pionnier sur le 4004.

Voir également

- Central Air Data Computer - le premier microprocesseur militaire 20 bits a été lancé en juin 1970 pour l' avion de chasse F-14 Tomcat de l' US Navy , environ un an et demi avant la sortie de l'Intel 4004

Remarques

Les références

Brevets

- US 3753011 14 août 1973. Faggin, Federico : Circuit bistable réglable d'alimentation.

- US 3821715 28 juin 1974. Hoff, Marcian; Mazor, Stanley ; Faggin, Federico : Système de mémoire pour ordinateur numérique à puces multiples.

Documents historiques

- Faggin, Federico; Capocaccia, F. "A New Integrated MOS Shift Register", Actes XV Congrès scientifique international de l'électronique, Rome, avril 1968, pp. 143-152. Cet article décrit un nouveau registre à décalage statique MOS, développé chez SGS-Fairchild (maintenant ST Micro) à la fin de 1967, avant que Federico Faggin ne rejoigne la R&D de Fairchild à Palo Alto (Ca) en février 1968. Faggin a ensuite utilisé ce nouveau registre à décalage dans les puces MCS-4, dont la 4004.

- Couverture et résumé du programme IEDM (International Electron Devices Meeting) (octobre 1968) . La technologie Silicon Gate (SGT) a été présentée pour la première fois par son développeur, Federico Faggin, à l'IEDM le 23 octobre 1968, à Washington, DC. plus tard universellement adopté par l'industrie des semi-conducteurs. Le SGT a été la première technologie à produire des RAM dynamiques commerciales, des capteurs d'images CCD, des mémoires non volatiles et le microprocesseur, fournissant pour la première fois tous les éléments fondamentaux d'un ordinateur à usage général avec des circuits intégrés LSI.

- Couverture de Electronics Magazine (29 septembre 1969) . L'article sur l'électronique présente le Fairchild 3708, conçu par Federico Faggin en 1968. C'était le premier circuit intégré commercial au monde utilisant la technologie Silicon Gate, prouvant sa viabilité.

- Initiales FF (Federico Faggin) sur le dessin 4004 (1971) . Le 4004 porte les initiales FF de son concepteur, Federico Faggin, gravées sur un coin de la puce. La signature de la puce était un geste spontané d'auteur fier et était également une idée originale imitée après lui par de nombreux concepteurs Intel.

- Busicom 141-PF Imprimante Calculatrice Ingénierie Prototype (1971) . (Don de Federico Faggin au Computer History Museum, Mountain View, CA). Le catalogue de la collection CHM présente des images du prototype d'ingénierie de la calculatrice de bureau Busicom 141-PF. Le prototype d'ingénierie utilisait le premier microprocesseur au monde jamais produit. Ce prototype unique en son genre était un cadeau personnel du président de Busicom, M. Yoshio Kojima, à Federico Faggin pour sa direction réussie de la conception et du développement du 4004 et de trois autres puces de mémoire et d'E/S (le chipset MCS-4 ). Après l'avoir conservé chez lui pendant 25 ans, Faggin l'a fait don au CHM en 1996.

- Federico Faggin et ME Hoff : « Les pièces standard et la conception personnalisée fusionnent dans un kit de processeur à quatre puces ». Electronics/24 avril 1972, p. 112-116. Réimprimé aux pages 6-27 à 6-31 de The Intel Memory Design Handbook : août 1973 .

- Federico Faggin, M. Shima, ME Hoff, Jr., H. Feeney, S. Mazor : "Le MCS-4—Un micro système informatique LSI". Conférence IEEE '72 Région Six. Réimprimé aux pages 6-32 à 6-37 de The Intel Memory Design Handbook : août 1973 .

Lectures complémentaires

- Federico Faggin, Marcian E. Hoff Jr., Stanley Mazor et Masatoshi Shima. L'histoire du 4004. IEEE Micro, 16(6):10-20, décembre 1996. "L'équipe de conception du 4004 raconte son histoire."

- 35e anniversaire du microprocesseur Intel 4004 - Enregistrement en direct des présentations de Ted Hoff et Federico Faggin au Computer History Museum pour le 35e anniversaire du premier microprocesseur. ( youtube.com )

- IEEE Solid State Circuits Magazine, Hiver 2009 Vol.1 No.1. « Le microprocesseur 4004 de Faggin, Hoff, Mazor et Shima ».

- La technologie MOS Silicon Gate et les premiers microprocesseurs , par Federico Faggin publié dans La Rivista del Nuovo Cimento, Italian Physical Society, Vol. 38, n° 12, 2015.

- "Comment nous avons fait le microprocesseur" par Federico Faggin. Nature Électronique, Vol. 1er janvier 2018. Publié en ligne : 2018-01-08

Liens externes

- Le premier microprocesseur d'Intel—l'Intel 4004 : entrée du musée Intel (archives d'entreprise d'Intel)

- L'Intel 4004 : un témoignage de Federico Faggin, concepteur du 4004 et développeur de sa technologie habilitante

- La nouvelle méthodologie de conception logique aléatoire utilisée dans le 4004 et dans tous les premiers microprocesseurs Intel

- Entretien avec Masatoshi Shima

- Fiche technique du micro-ordinateur MCS-4 (12 pages)

- Intel 4004 - 45th Anniversary Project , Schematics sur le site Web non officiel 4004 et un simulateur en Java. Répliques à l'échelle 130x entièrement fonctionnelles du 4004 construites à l'aide de transistors discrets.

- Le rôle crucial de la conception en silicium dans l'invention du microprocesseur

- Images au microscope optique à haute résolution d'une puce Intel 4004 avec une explication de base de la logique CMOS

- Émulateur, assembleur et désassembleur Intel 4004 : outils de programmation simples pour Intel 4004 en Javascript

- Fiche technique Intel 4004

- Fiche technique Intel MCS-4

- Schéma BuscomV2p1

- Manuel de programmation du langage assembleur MSC-4

- Temple de la renommée des puces : Microprocesseur Intel 4004 ( site Web IEEE Spectrum )

- Histoire de l'Intel 4004