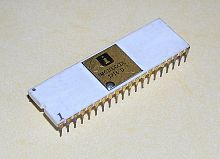

Intersil 6100 - Intersil 6100

L' Intersil 6100 est une implémentation à microprocesseur à puce unique du jeu d'instructions PDP-8 12 bits , ainsi qu'une gamme de circuits intégrés de prise en charge des périphériques et de mémoire développés par Intersil au milieu des années 1970. Il était parfois appelé CMOS-PDP8 . Puisqu'il était également produit par Harris Corporation , il était également connu sous le nom de Harris HM-6100 . L'Intersil 6100 a été introduit au deuxième trimestre de 1975 et la version Harris en 1976.

La famille 6100 a été produite en utilisant CMOS plutôt que les technologies bipolaires et NMOS utilisées par la plupart de ses contemporains ( Z80 , 8080 , 6502 , 6800 , 9900 , etc.). En raison de sa technologie CMOS et de sa faible vitesse d'horloge, 8 MHz pour le Harris HM-6100A, il avait une consommation d'énergie relativement faible, moins de 100 mW à 10 V / 2 MHz, et pouvait être exploité à partir d'une seule alimentation sur le large. plage de 4 à 11 V. Ainsi, il pourrait être utilisé dans des systèmes embarqués à haute fiabilité sans nécessiter de gestion thermique significative, si le reste du système était également CMOS.

Le 6100 était disponible selon les spécifications militaires, et comme il était à double source par Intersil et Harris, il était utilisé dans certains produits militaires comme une alternative de faible puissance aux 8080, 6800 etc. Bien qu'il ait un jeu d'instructions et une architecture très simples, il était parfaitement adapté à une utilisation dans des systèmes embarqués qui utilisaient auparavant des circuits logiques discrets et même des commutateurs rotatifs motorisés Ledex ou des contrôleurs logiques à relais.

La famille 6100 a été utilisée dans un certain nombre de produits commerciaux, y compris la gamme DECmate , la première tentative de DEC de produire un ordinateur personnel . Intersil a vendu les circuits intégrés commercialement jusqu'en 1982 sous le nom de famille IM6100. Son prix n'était pas compétitif et l'offre a échoué. Les PC IBM en 1981 ont cimenté la ruine des «CMOS-8».

Description

Le 6100 est un processeur 12 bits qui émule étroitement le PDP-8 (voir PDP-8 pour une discussion plus complète). Il dispose de trois registres principaux: PC ( compteur de programme ), AC 12 bits ( accumulateur ) et MQ (Quotient multiplicateur). Toutes les instructions à deux opérandes lisent l'AC et le MQ et réécrivent sur l'AC. Il n'y a pas de pointeur de pile; les sous-programmes retournent à leurs appelants en retournant au code principal, généralement en stockant l'adresse de retour dans le premier mot du sous-programme lui-même. (Pas bon pour les programmes en ROM.)

Les conditions dans le 6100 permettent de sauter uniquement l'instruction suivante. Les branches sont construites avec un saut conditionnel et un saut suivant. Il n'y a qu'une seule interruption masquable. Lorsque l'interruption est déclenchée, la CPU stocke le PC actuel en 0000, puis commence à s'exécuter à partir de 0001. L'interruption peut être désactivée ou activée à l'aide des instructions IOF et ION (ou SKON).

Le 6100 dispose d'un bus de données / d'adresses de 12 bits, limitant la RAM à seulement 4K mots (6 Ko). Les références de mémoire sont de 7 bits, décalées soit de l'adresse 0, soit de l'adresse de base de la page PC (obtenue en mettant les sept bits les moins significatifs de PC à zéro). La mémoire pouvait être étendue à l'aide de la puce de support optionnelle 6102, qui ajoutait trois lignes d'adresse et donc une mémoire étendue à 32K mots (48 Ko) de la même manière que le PDP-8 / E étendait le PDP-8. Le 6102 possède deux registres internes, IFR (registre de champ d'instructions) et DFR (registre de champ de données), qui décalent la page 4K lorsque le processeur accède à la mémoire.

Versions et matériel de support

Intersil a offert une variété de puces associées pour prendre en charge les systèmes 6100. Le CPU IM6100 implémente un straight-8 (PDP-8 de base sans matériel de mappage de mémoire). L'IM6101 PIE (élément d'interface programmable) est un port d'E / S PDP-8 de base. L'IM6102 MEDIC (Memory Extension, DMA Controller, Interval Timer) convertit un IM6100 en quelque chose qui ressemble au CPU d'un PDP-8 / E. L'IM6103 PIO (port d'entrée-sortie parallèle) et l'IM6402 ou l'IM6403 UART sont des dispositifs d'E / S PDP-8 de base sur les circuits intégrés.

Intersil a également proposé des tailles compatibles de RAM et ROM : le IM6551 et IM6561 (1 Kbit, 256 × 4) SRAM , le IM6512 (768 Bit, 64x12) SRAM , et le IM6312 (12 Kbit, 1024 × 12) masque programmable PROM .

Une sélection de ces composants était proposée sous forme de kit d'échantillonneur de la famille CMOS Intersil 6801 avec la carte de circuit imprimé 6960 - Sampler, un système à carte unique comprenant le processeur IM6100, IM6101 PIE, la ROM de moniteur IM6312 ODT (Octal Debugging Technique) , trois 256 × 4 CMOS RAM et un UART IM6403.

Le 6100 de base a ensuite été mis à niveau vers le 6120, avec le contrôleur de mémoire 6102 intégré.

Les références

Liens externes

- «Architecture de microprocesseur Intersil 6100» , CPU World

- Intersil, "Échantillonneur de la famille CMOS IM6100"