PUISSANCE5 - POWER5

| informations générales | |

|---|---|

| Lancé | 2004 |

| Conçu par | IBM |

| Performance | |

| Max. Fréquence d'horloge du processeur | 1,5 GHz à 2,3 GHz |

| Cacher | |

| Cache L1 | 32+32 Ko/cœur |

| Cache L2 | 1,875 Mo/puce |

| Cache L3 | 36 Mo/puce (hors puce) |

| Architecture et classement | |

| Min. taille de la caractéristique | 130 nm à 90 nm |

| Jeu d'instructions | PowerPC 2.02 |

| Spécifications physiques | |

| Noyaux | |

| Histoire | |

| Prédécesseur | PUISSANCE4 |

| Successeur | PUISSANCE6 |

| Architectures POWER , PowerPC et Power ISA |

|---|

| NXP (anciennement Freescale et Motorola) |

| IBM |

|

| IBM/Nintendo |

| Autre |

| Liens connexes |

| Annulé en gris , historique en italique |

Le POWER5 est un microprocesseur développé et fabriqué par IBM . Il s'agit d'une version améliorée du POWER4 . Les principales améliorations sont la prise en charge du multithreading simultané (SMT) et un contrôleur de mémoire intégré . Le POWER5 est un microprocesseur double cœur , chaque cœur prenant en charge un fil physique et deux fils logiques, pour un total de deux fils physiques et quatre fils logiques.

Histoire

Les détails techniques du microprocesseur ont été présentés pour la première fois lors de la conférence Hot Chips de 2003 . Une description plus complète a été donnée au Microprocessor Forum 2003 le 14 octobre 2003. Le POWER5 n'était pas vendu ouvertement et était utilisé exclusivement par IBM et ses partenaires. Les systèmes utilisant le microprocesseur ont été introduites en 2004. Le POWER5 concurrence sur le marché des serveurs d'entreprise haut de gamme, principalement contre Intel Itanium 2 et dans une moindre mesure, le Sun Microsystems UltraSPARC IV et le Fujitsu SPARC64 V . Il a été remplacé en 2005 par une itération améliorée, le POWER5+.

La description

Le POWER5 est un développement ultérieur du POWER4 . L'ajout du multithreading bidirectionnel nécessitait la duplication de la pile de retour, du compteur de programme , du tampon d'instructions, de l'unité d'achèvement de groupe et de la file d'attente de stockage afin que chaque thread puisse avoir le sien. La plupart des ressources, telles que les fichiers de registres et les unités d'exécution, sont partagées, bien que chaque thread voit son propre ensemble de registres. Le POWER5 implémente le multithreading simultané (SMT), où deux threads sont exécutés simultanément. Le POWER5 peut désactiver SMT pour optimiser la charge de travail actuelle.

Comme de nombreuses ressources telles que les fichiers de registre sont partagées par deux threads, leur capacité est augmentée dans de nombreux cas pour compenser la perte de performances. Le nombre de registres entiers et à virgule flottante est augmenté à 120 chacun, à partir de 80 registres entiers et 72 registres à virgule flottante dans le POWER4. La capacité du cache d'instructions à virgule flottante est également augmentée de 20 à 24 entrées. La capacité du cache unifié L2 a été augmentée à 1,875 Mo et l' associativité définie à 10 voies. Le cache L3 unifié a été intégré à l'emballage au lieu d'être situé à l'extérieur dans des puces séparées. Sa capacité a été augmentée à 36 Mo. Comme le POWER4, le cache est partagé par les deux cœurs. Le cache est accessible via deux bus 128 bits unidirectionnels fonctionnant à la moitié de la fréquence du cœur.

Le contrôleur de mémoire intégré prend en charge jusqu'à 64 Go de mémoire DDR et DDR2 . Il utilise des bus série haute fréquence pour communiquer avec des tampons externes qui interfacent les modules de mémoire double en ligne (DIMM) avec le microprocesseur.

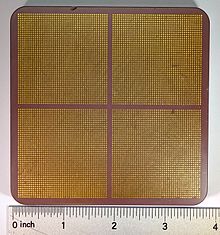

Le POWER5 contient 276 millions de transistors et a une superficie de 389 mm 2 . Il est fabriqué par IBM dans un procédé de 0,13 m de silicium sur isolant (SOI) complémentaire métal-oxyde-semiconducteur (CMOS) avec huit couches d' interconnexion en cuivre . La puce POWER5 est conditionnée soit dans un module à double puce (DCM) soit dans un module à puces multiples (MCM). Le DCM contient une matrice POWER5 et sa matrice de cache L3 associée. Le MCM contient quatre matrices POWER5 et quatre matrices de cache L3, une pour chaque matrice POWER5, et mesure 95 mm sur 95 mm.

Plusieurs processeurs POWER5 dans des systèmes haut de gamme peuvent être couplés ensemble pour agir comme un seul processeur vectoriel grâce à une technologie appelée ViVA (Virtual Vector Architecture).

PUISSANCE5+

Le POWER5+ est une itération améliorée du POWER5 introduit le 4 octobre 2005. Les améliorations étaient initialement une consommation d'énergie inférieure, en raison du processus plus récent dans lequel elle a été fabriquée. La puce POWER5+ utilise un processus de fabrication de 90 nm. Cela a entraîné la diminution de la taille de 389 mm meurent 2 à 243 mm 2 .

La fréquence d'horloge n'a pas été augmentée au lancement et est restée comprise entre 1,5 et 1,9 GHz. Le 14 février 2006, de nouvelles versions ont porté la fréquence d'horloge à 2,2 GHz puis à 2,3 GHz le 25 juillet 2006.

Le POWER5+ était emballé dans les mêmes boîtiers que les microprocesseurs POWER5 précédents, mais était également disponible dans un module à quatre puces (QCM) contenant deux matrices POWER5+ et deux matrices de cache L3, une pour chaque matrice POWER5+. Ces puces QCM fonctionnaient à une fréquence d'horloge comprise entre 1,5 et 1,8 GHz.

Utilisateurs

IBM utilise les microprocesseurs DCM et MCM POWER5 dans ses familles de serveurs System p et System i , dans son serveur de stockage DS8000 et comme microprocesseurs intégrés dans ses imprimantes Infoprint haut de gamme. Les microprocesseurs DCM POWER5 sont utilisés par IBM dans sa station de travail haut de gamme IntelliStation POWER 285 . Les utilisateurs tiers des microprocesseurs POWER5 sont Groupe Bull , dans ses serveurs Escala, et Hitachi, dans ses ordinateurs SR11000 avec jusqu'à 128 microprocesseurs POWER5+, qui ont plusieurs installations figurant dans la liste 2007 TOP500 des supercalculateurs. IBM utilise le POWER5+ QCM dans ses serveurs System p5 510Q, 520Q, 550Q et 560Q.

Remarques

Voir également

Les références

- "IBM Aperçus Power5". (8 septembre 2003). Rapport du microprocesseur .

- Clabes, Joachim et al. (2004). "Conception et mise en œuvre du microprocesseur POWER5". Actes de 2004 IEEE International Solid-State Circuits Conference .

- Glaskowsky, Peter N. (14 octobre 2003). "IBM lève le rideau sur Power5". Rapport du microprocesseur .

- Kalla, Ron ; Sinharoy, Balaram ; Tendler, Joel M. (2004). "Puce IBM Power5 : Un processeur multithread à deux cœurs". IEEE Micro .

- Krewell, Kevin (22 décembre 2003). "Power5 Tops sur la bande passante". Rapport du microprocesseur .

- Sinharoy, Balaram et al. (2005). "Microarchitecture du système POWER5". Revue IBM de recherche et développement .

- Vance, Ashlee (4 octobre 2005). "IBM pompe la ligne Unix pleine de Power5+" . Le Registre .

Liens externes

- Sizing up the Super Heavyweights , une comparaison et une analyse du POWER5 et Montecito, qui explique les changements majeurs entre le POWER4 au POWER5, ainsi que des estimations de performances

- Un cluster IBM Power5+ p5-575 hautes performances 1600 et un stockage DDN S2A9550 , Texas A&M University