Mémoire à changement de phase - Phase-change memory

La mémoire à changement de phase (également appelée PCM , PCME , PRAM , PCRAM , OUM ( mémoire unifiée ovonique ) et C-RAM ou CRAM ( chalcogénure RAM )) est un type de mémoire vive non volatile . Les PRAM exploitent le comportement unique du verre chalcogénure . Dans l'ancienne génération de PCM, la chaleur produite par le passage d'un courant électrique à travers un élément chauffant généralement en nitrure de titane était utilisée soit pour chauffer et tremper rapidement le verre, le rendant amorphe , soit pour le maintenir dans sa plage de température de cristallisation pendant un certain temps, le faisant ainsi passer à un état cristallin . PCM a également la capacité d'atteindre un certain nombre d'états intermédiaires distincts, ayant ainsi la capacité de contenir plusieurs bits dans une seule cellule, mais les difficultés de programmation des cellules de cette manière ont empêché ces capacités d'être mises en œuvre dans d'autres technologies (notamment flash mémoire ) avec la même capacité.

La nouvelle technologie PCM a évolué dans deux directions différentes. Un groupe a dirigé de nombreuses recherches pour tenter de trouver des alternatives matérielles viables au Ge 2 Sb 2 Te 5 (GST), avec un succès mitigé. Un autre groupe a développé l'utilisation d'un super-réseau GeTe-Sb 2 Te 3 pour obtenir des changements de phase non thermiques en changeant simplement l'état de coordination des atomes de germanium avec une impulsion laser. Cette nouvelle mémoire interfaciale à changement de phase (IPCM) a connu de nombreux succès et continue d'être le site de nombreuses recherches actives.

Leon Chua a fait valoir que tous les dispositifs à mémoire non volatile à deux terminaux, y compris le PCM, devraient être considérés comme des memristors . Stan Williams de HP Labs a également soutenu que le PCM devrait être considéré comme un memristor . Cependant, cette terminologie a été contestée et l'applicabilité potentielle de la théorie des memristors à tout dispositif physiquement réalisable est sujette à caution.

Arrière-plan

Dans les années 1960, Stanford R. Ovshinsky de Energy Conversion Devices a d'abord exploré les propriétés des verres de chalcogénure en tant que technologie de mémoire potentielle. En 1969, Charles Sie a publié une thèse à l'Iowa State University qui décrivait et démontrait la faisabilité d'un dispositif de mémoire à changement de phase en intégrant un film de chalcogénure à un réseau de diodes . Une étude cinématographique en 1970 a établi que le mécanisme de mémoire de changement de phase dans le verre chalcogénure implique la croissance de filaments cristallins induite par un champ électrique. Dans le numéro de septembre 1970 d' Electronics , Gordon Moore , co-fondateur d' Intel , a publié un article sur la technologie. Cependant, des problèmes de qualité des matériaux et de consommation d'énergie ont empêché la commercialisation de la technologie. Plus récemment, l'intérêt et la recherche ont repris car les technologies de mémoire flash et DRAM devraient rencontrer des difficultés de mise à l'échelle à mesure que la lithographie des puces se rétrécit.

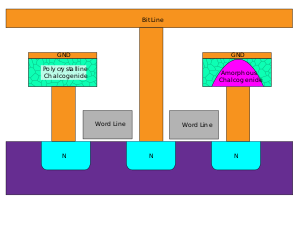

Les états cristallin et amorphe du verre chalcogénure ont des valeurs de résistivité électrique radicalement différentes . L'état amorphe à haute résistance représente un 0 binaire , tandis que l'état cristallin à faible résistance représente un 1. Le chalcogénure est le même matériau utilisé dans les supports optiques réinscriptibles (tels que les CD-RW et DVD-RW ). Dans ces cas, les propriétés optiques du matériau sont manipulées, plutôt que sa résistivité électrique, car l' indice de réfraction du chalcogénure change également avec l'état du matériau.

Bien que la PRAM n'ait pas encore atteint le stade de la commercialisation pour les appareils électroniques grand public, presque tous les prototypes d'appareils utilisent un alliage de chalcogénure de germanium , d' antimoine et de tellure ( GeSbTe ) appelé GST. La stoechiométrie ou le rapport des éléments Ge:Sb:Te est de 2:2:5. Lorsque la GST est chauffée à une température élevée (plus de 600 °C), sa cristallinité de chalcogénure est perdue. Une fois refroidi, il est congelé dans un état semblable à du verre amorphe et sa résistance électrique est élevée. En chauffant le chalcogénure à une température supérieure à son point de cristallisation , mais inférieure au point de fusion , il se transformera en un état cristallin avec une résistance beaucoup plus faible. Le temps nécessaire pour terminer cette transition de phase dépend de la température. Les parties plus froides du chalcogénure mettent plus de temps à cristalliser et les parties surchauffées peuvent être refondues. Une échelle de temps de cristallisation de l'ordre de 100 ns est couramment utilisée. C'est plus long que les dispositifs de mémoire volatile conventionnels comme les DRAM modernes , qui ont un temps de commutation de l'ordre de deux nanosecondes. Cependant, une demande de brevet de Samsung Electronics en janvier 2006 indique que la PRAM peut atteindre des temps de commutation aussi rapides que cinq nanosecondes.

Une avancée plus récente mise au point par Intel et ST Microelectronics permet de contrôler plus soigneusement l'état du matériau, ce qui lui permet de se transformer en l'un des quatre états distincts ; les états amorphes ou cristallins précédents, ainsi que deux nouveaux états partiellement cristallins. Chacun de ces états a des propriétés électriques différentes qui peuvent être mesurées lors des lectures, permettant à une seule cellule de représenter deux bits, doublant ainsi la densité de la mémoire.

PRAM vs Flash

Le temps de commutation de la PRAM et son évolutivité inhérente la rendent très attrayante. La sensibilité à la température de la PRAM est peut-être son inconvénient le plus notable, qui peut nécessiter des changements dans le processus de production des fabricants intégrant la technologie.

La mémoire flash fonctionne en modulant la charge ( électrons ) stockée dans la grille d'un transistor MOS . La grille est construite avec une "pile" spéciale conçue pour piéger les charges (soit sur une grille flottante, soit dans des "pièges" isolants ). La présence de charge au sein de la grille décale la tension de seuil du transistor , supérieure ou inférieure, correspondant à un 1 à 0, par exemple. Changer l'état du bit nécessite de supprimer la charge accumulée, ce qui nécessite une tension relativement élevée pour "aspirer" les électrons de la grille flottante. Ce sursaut de tension est fourni par une pompe de charge , qui met un certain temps à accumuler de la puissance. Les temps d'écriture généraux pour les périphériques Flash courants sont de l'ordre de 100 s (pour un bloc de données), environ 10 000 fois le temps de lecture typique de 10 ns, pour la SRAM par exemple (pour un octet).

La PRAM peut offrir des performances beaucoup plus élevées dans les applications où l'écriture rapide est importante, à la fois parce que l'élément de mémoire peut être commuté plus rapidement, et également parce que des bits uniques peuvent être modifiés en 1 ou 0 sans avoir besoin d'effacer d'abord un bloc entier de cellules. Les hautes performances de la PRAM, des milliers de fois plus rapides que les disques durs conventionnels, la rendent particulièrement intéressante dans les rôles de mémoire non volatile dont les performances sont actuellement limitées par le temps d'accès à la mémoire.

De plus, avec Flash, chaque sursaut de tension aux bornes de la cellule provoque une dégradation. À mesure que la taille des cellules diminue, les dommages causés par la programmation s'aggravent car la tension nécessaire pour programmer l'appareil ne s'adapte pas à la lithographie. La plupart des périphériques flash sont actuellement évalués pour seulement 5 000 écritures par secteur, et de nombreux contrôleurs flash effectuent un nivellement de l'usure pour répartir les écritures sur de nombreux secteurs physiques.

Les périphériques PRAM se dégradent également avec l'utilisation, pour des raisons différentes de celles de Flash, mais se dégradent beaucoup plus lentement. Un périphérique PRAM peut supporter environ 100 millions de cycles d'écriture. La durée de vie de la PRAM est limitée par des mécanismes tels que la dégradation due à la dilatation thermique de la GST pendant la programmation, la migration du métal (et d'autres matériaux) et d'autres mécanismes encore inconnus.

Les pièces flash peuvent être programmées avant d'être soudées sur une carte , ou même achetées préprogrammées. Le contenu d'une PRAM, cependant, est perdu en raison des températures élevées nécessaires pour souder l'appareil à une carte (voir soudure par refusion ou soudure à la vague ). Ceci est aggravé par la récente tendance à la fabrication sans plomb nécessitant des températures de soudage plus élevées. Le fabricant utilisant des pièces de PRAM doit fournir un mécanisme pour programmer la PRAM "dans le système" après qu'elle ait été soudée en place.

Les portes spéciales utilisées dans la mémoire Flash se chargent de "fuites" (électrons) au fil du temps, provoquant une corruption et une perte de données. La résistivité de l'élément mémoire dans la PRAM est plus stable ; à la température de fonctionnement normale de 85 °C, il devrait conserver les données pendant 300 ans.

En modulant soigneusement la quantité de charge stockée sur la porte, les dispositifs Flash peuvent stocker plusieurs (généralement deux) bits dans chaque cellule physique. En effet, cela double la densité de la mémoire, réduisant ainsi les coûts. Les périphériques PRAM ne stockaient à l'origine qu'un seul bit dans chaque cellule, mais les récentes avancées d'Intel ont supprimé ce problème.

Étant donné que les dispositifs Flash piègent les électrons pour stocker des informations, ils sont susceptibles d'être corrompus par les rayonnements, ce qui les rend inadaptés à de nombreuses applications spatiales et militaires. PRAM présente une résistance plus élevée au rayonnement.

Les sélecteurs de cellules PRAM peuvent utiliser divers dispositifs : diodes , BJT et MOSFET . L'utilisation d'une diode ou d'un BJT fournit la plus grande quantité de courant pour une taille de cellule donnée. Cependant, le problème lié à l'utilisation d'une diode provient des courants parasites vers les cellules voisines, ainsi que d'une exigence de tension plus élevée, entraînant une consommation d'énergie plus élevée. La résistance du chalcogénure étant une résistance nécessairement plus grande que la diode, la tension de fonctionnement doit dépasser largement 1 V pour garantir un courant de polarisation direct adéquat de la diode. La conséquence peut-être la plus grave de l'utilisation d'un réseau sélectionné par diode, en particulier pour les grands réseaux, est le courant de fuite de polarisation inverse total des lignes de bits non sélectionnées. Dans les réseaux sélectionnés par transistor, seules les lignes de bits sélectionnées contribuent au courant de fuite de polarisation inverse. La différence de courant de fuite est de plusieurs ordres de grandeur. Une autre préoccupation concernant la mise à l'échelle en dessous de 40 nm est l'effet des dopants discrets lorsque la largeur de la jonction pn diminue. Les sélecteurs à couche mince permettent des densités plus élevées, en utilisant une zone de cellule < 4 F 2 en empilant les couches de mémoire horizontalement ou verticalement. Souvent, les capacités d'isolement sont inférieures à l'utilisation de transistors si le rapport marche/arrêt du sélecteur n'est pas suffisant, limitant la possibilité de faire fonctionner de très grands réseaux dans cette architecture. Le commutateur de seuil à base de chalcogénure a été démontré comme un sélecteur viable pour les matrices PCM haute densité

2000 et après

En août 2004, Nanochip a licencié la technologie PRAM pour une utilisation dans les dispositifs de stockage de sondes MEMS (systèmes micro-électriques-mécaniques). Ces appareils ne sont pas à semi-conducteurs. Au lieu de cela, un très petit plateau recouvert de chalcogénure est traîné sous de nombreuses (des milliers voire des millions) de sondes électriques capables de lire et d'écrire le chalcogénure. La technologie de micro-mover de Hewlett-Packard peut positionner avec précision le plateau à 3 nm afin que des densités de plus de 1 Tbit (125 Go) par pouce carré soient possibles si la technologie peut être perfectionnée. L'idée de base est de réduire la quantité de câblage nécessaire sur la puce ; au lieu de câbler chaque cellule, les cellules sont rapprochées et lues par le courant passant à travers les sondes MEMS, agissant comme des fils. Cette approche ressemble beaucoup à la technologie Millipede d'IBM .

Cellule Samsung 46,7 nm

En septembre 2006, Samsung a annoncé un prototype d'appareil de 512 Mo (64 Mo) utilisant des commutateurs à diodes. L'annonce était quelque peu surprenante, et elle était particulièrement remarquable pour sa densité assez élevée. Le prototype présentait une taille de cellule de seulement 46,7 nm, plus petite que les appareils Flash commerciaux disponibles à l'époque. Bien que des périphériques Flash de plus grande capacité soient disponibles (64 Go, ou 8 Go, venaient juste d'arriver sur le marché), d'autres technologies concurrentes pour remplacer Flash offraient en général des densités plus faibles (taille de cellule plus grande). Les seuls périphériques MRAM et FeRAM de production ne font que 4 Mo, par exemple. La haute densité du prototype de périphérique PRAM de Samsung a suggéré qu'il pourrait être un concurrent Flash viable, et non limité à des rôles de niche comme l'ont été d'autres périphériques. La PRAM semblait être particulièrement attrayante en tant que remplacement potentiel de la Flash NOR, où les capacités des périphériques sont généralement inférieures à celles des périphériques Flash NAND . (Les capacités de pointe sur la NAND ont dépassé 512 Mo il y a quelque temps.) NOR Flash offre des densités similaires à celles du prototype PRAM de Samsung et offre déjà une adressabilité de bits (contrairement à la NAND où la mémoire est accessible par banques de plusieurs octets à la fois).

PRAM d'Intel

L'annonce de Samsung a été suivie par celle d' Intel et de STMicroelectronics , qui ont présenté leurs propres périphériques PRAM lors du Forum des développeurs Intel 2006 en octobre. Ils ont montré une pièce de 128 Mo dont la fabrication a commencé dans le laboratoire de recherche de STMicroelectronics à Agrate, en Italie. Intel a déclaré que les appareils étaient strictement une preuve de concept.

Appareil BAE

La PRAM est également une technologie prometteuse dans les industries militaire et aérospatiale où les effets des rayonnements rendent l'utilisation de mémoires non volatiles standard telles que Flash impraticable. Les dispositifs de mémoire PRAM ont été introduits par BAE Systems , appelés C-RAM, revendiquant une excellente tolérance aux radiations ( rad-hard ) et une immunité au verrouillage . De plus, BAE revendique une endurance de cycle d'écriture de 10 8 , ce qui lui permettra d'être un candidat au remplacement des PROM et des EEPROM dans les systèmes spatiaux.

Cellule à plusieurs niveaux

En février 2008, Intel et STMicroelectronics ont dévoilé le premier prototype de matrice PRAM multiniveau ( MLC ). Le prototype stockait deux bits logiques dans chaque cellule physique, en fait 256 Mo de mémoire stockés dans une matrice physique de 128 Mo. Cela signifie qu'au lieu des deux états normaux - entièrement amorphe et entièrement cristallin - deux états intermédiaires distincts supplémentaires représentent différents degrés de cristallisation partielle, permettant de stocker deux fois plus de bits dans la même zone physique. En juin 2011, IBM a annoncé avoir créé une mémoire à changement de phase multi-bits stable, fiable, offrant des performances et une stabilité élevées.

Le périphérique 90 nm d'Intel

Toujours en février 2008, Intel et STMicroelectronics ont expédié des échantillons prototypes de leur premier produit PRAM à leurs clients. Le produit 90 nm, 128 Mo (16 Mo) s'appelait Alverstone.

En juin 2009, Samsung et Numonyx BV ont annoncé un effort de collaboration dans le développement de produits matériels adaptés au marché PRAM.

En avril 2010, Numonyx a annoncé la gamme Omneo de mémoires à changement de phase compatibles NOR 128 Mbit. Samsung a annoncé la livraison de 512 Mo de RAM à changement de phase (PRAM) dans un boîtier multi-puces (MCP) pour une utilisation dans les combinés mobiles d'ici l'automne 2010.

Aluminium/antimoine

Les dispositifs de mémoire à changement de phase à base de germanium, d'antimoine et de tellure présentent des défis de fabrication, car la gravure et le polissage du matériau avec des chalcogènes peuvent modifier la composition du matériau. Les matériaux à base d'Al et de Sb sont plus stables thermiquement que le Ge-Sb-Te. Al 50 Sb 50 a trois niveaux de résistance distincts, offrant la possibilité de stocker trois bits de données dans deux cellules au lieu de deux (neuf états possibles pour la paire de cellules, l'utilisation de huit de ces états donne log 2 8 = 3 bits).

Défis

Le plus grand défi pour la mémoire à changement de phase a été l'exigence d'une densité de courant de programmation élevée (>10 7 A/cm², comparé à 10 5 ...10 6 A/cm² pour un transistor ou une diode typique). Le contact entre la région à changement de phase chaude et le diélectrique adjacent est une autre préoccupation fondamentale. Le diélectrique peut commencer à laisser échapper du courant à une température plus élevée, ou peut perdre son adhérence lorsqu'il se dilate à une vitesse différente de celle du matériau à changement de phase.

La mémoire à changement de phase est susceptible d'un compromis fondamental entre un changement de phase involontaire et prévu. Cela provient principalement du fait que le changement de phase est un processus thermique plutôt qu'un processus électronique. Les conditions thermiques qui permettent une cristallisation rapide ne doivent pas être trop similaires aux conditions de veille, par exemple la température ambiante. Sinon, la conservation des données ne peut pas être maintenue. Avec l'énergie d'activation appropriée pour la cristallisation, il est possible d'avoir une cristallisation rapide dans des conditions de programmation tout en ayant une cristallisation très lente dans des conditions normales.

Le plus grand défi pour la mémoire à changement de phase est probablement sa résistance à long terme et sa dérive de tension de seuil. La résistance de l'état amorphe augmente lentement selon une loi de puissance (~t 0,1 ). Cela limite considérablement la capacité de fonctionnement à plusieurs niveaux (un état intermédiaire inférieur serait confondu avec un état intermédiaire supérieur ultérieurement) et pourrait également compromettre le fonctionnement standard à deux états si la tension de seuil augmente au-delà de la valeur de conception.

En avril 2010, Numonyx a lancé sa gamme Omneo de puces PRAM de remplacement flash 128 Mo d'interface série et parallèle NOR . Bien que les puces flash NOR qu'ils avaient l'intention de remplacer fonctionnaient dans la plage de -40 à 85 °C, les puces PRAM fonctionnaient dans la plage de 0 à 70 °C, indiquant une fenêtre de fonctionnement plus petite par rapport au flash NOR. Cela est probablement dû à l'utilisation de jonctions p–n hautement sensibles à la température pour fournir les courants élevés nécessaires à la programmation.

Chronologie

- Janvier 1955 : Kolomiets et Gorunova révèlent les propriétés semi-conductrices des verres chalcogénures .

- Septembre 1966 : Stanford Ovshinsky dépose le premier brevet sur la technologie à changement de phase

- Janvier 1969 : Charles H. Sie publie une thèse à l'Iowa State University sur le dispositif de mémoire à changement de phase au chalcogénure

- Juin 1969 : le brevet américain 3 448 302 (Shanefield) licencié à Ovshinsky revendique le premier fonctionnement fiable du périphérique PRAM

- Septembre 1970 : Gordon Moore publie des recherches dans Electronics Magazine

- Juin 1999 : La coentreprise Ovonyx est formée pour commercialiser la technologie PRAM

- Novembre 1999 : Lockheed Martin travaille avec Ovonyx sur PRAM pour des applications spatiales

- Février 2000 : Intel investit dans Ovonyx, licencie la technologie

- Décembre 2000 : ST Microelectronics licencie la technologie PRAM d'Ovonyx

- Mars 2002 : Macronix dépose une demande de brevet pour la PRAM sans transistor

- Juillet 2003 : Samsung commence à travailler sur la technologie PRAM

- 2003 à 2005 : demandes de brevet liées à la PRAM déposées par Toshiba, Hitachi, Macronix, Renesas, Elpida, Sony, Matsushita, Mitsubishi, Infineon et plus

- Août 2004 : Nanochip licencie la technologie PRAM d'Ovonyx pour une utilisation dans le stockage des sondes MEMS

- Août 2004 : Samsung annonce le succès d'une baie PRAM 64 Mbit

- Février 2005 : Elpida licencie la technologie PRAM d'Ovonyx

- Septembre 2005 : Samsung annonce le succès d'une baie PRAM de 256 Mbits, vante un courant de programmation de 400 μA

- Octobre 2005 : Intel augmente ses investissements dans Ovonyx

- décembre 2005 ; Hitachi et Renesas annoncent une PRAM 1,5 V avec un courant de programmation de 100 A

- Décembre 2005 : Samsung licencie la technologie PRAM d'Ovonyx

- Juillet 2006 : BAE Systems commercialise la première puce PRAM commerciale

- Septembre 2006 : Samsung annonce une PRAM 512 Mbit

- Octobre 2006 : Intel et STMicroelectronics présentent une puce PRAM 128 Mbit

- Décembre 2006 : IBM Research Labs démontre un prototype 3 par 20 nanomètres

- Janvier 2007 : Qimonda licencie la technologie PRAM d'Ovonyx

- Avril 2007 : Justin Rattner, directeur de la technologie d'Intel, s'apprête à faire la première démonstration publique de la technologie PRAM (RAM à changement de phase) de l'entreprise

- Octobre 2007 : Hynix commence à poursuivre la PRAM en licenciant la technologie d'Ovonyx

- Février 2008 : Intel et STMicroelectronics annoncent la PRAM MLC à quatre états et commencent à envoyer des échantillons aux clients.

- Décembre 2008 : Numonyx annonce un dispositif PRAM 128 Mbit de production en série à un client sélectionné.

- Juin 2009 : La RAM à changement de phase de Samsung entrera en production de masse à partir de juin

- Septembre 2009 : Samsung annonce le démarrage de la production en série d'un périphérique PRAM 512 Mbit

- Octobre 2009 : Intel et Numonyx annoncent avoir trouvé un moyen d'empiler des matrices de mémoire à changement de phase sur une seule puce

- Décembre 2009 : Numonyx annonce un produit 1 Go 45 nm

- Avril 2010 : Numonyx sort la série Omneo PRAM (P8P et P5Q), toutes deux en 90 nm.

- Avril 2010 : Samsung sort une PRAM 512Mbit avec un processus 65 nm, en Multi-Chip-Package.

- Février 2011 : Samsung présente la PRAM 58 nm 1.8V 1Gb.

- Février 2012 : Samsung présente la PRAM 20 nm 1.8V 8Gb

- Juillet 2012 : Micron annonce la disponibilité de la mémoire à changement de phase pour les appareils mobiles - la première solution PRAM en production de volume

- Janvier 2014 : Micron retire du marché toutes les pièces PCM.

- Mai 2014 : IBM démontre la combinaison du PCM, de la NAND conventionnelle et de la DRAM sur un seul contrôleur

- Août 2014 : Western Digital présente un prototype de stockage PCM avec 3 millions d'E/S et une latence de 1,5 microseconde

- Juillet 2015 : Intel et Micron ont annoncé la mémoire 3D Xpoint où un alliage à changement de phase est utilisé comme partie de stockage d'une cellule de mémoire.

Voir également

- RAM ferroélectrique (FRAM)

- Mémoire vive magnétorésistive (MRAM)

- Mémoire morte (RMM)

Les références

Liens externes

- Micron

- Ovonyx, Inc.

- Dispositifs de conversion d'énergie, Inc.

- PRAM basse consommation Hitachi/Renesas

- Stockage des sondes Hewlett-Packard

- Symposium Européen\Changement de Phase et Ovoniques

- Communiqué de presse BAE C-RAM NVM durci aux radiations

- Fiche technique NVM durcie aux radiations BAE C-RAM

- Introduction au PCM par Numonyx (vidéo)