PUISSANCE2 - POWER2

| informations générales | |

|---|---|

| Lancé | 1993 |

| Conçu par | IBM |

| Architecture et classement | |

| Jeu d'instructions | PUISSANCE ISA |

| Histoire | |

| Prédécesseur | PUISSANCE1 |

| Successeur | PUISSANCE3 |

| Architectures POWER , PowerPC et Power ISA |

|---|

| NXP (anciennement Freescale et Motorola) |

| IBM |

|

| IBM/Nintendo |

| Autre |

| Liens connexes |

| Annulé en gris , historique en italique |

Le POWER2 , nommé à l'origine RIOS2 , est un processeur conçu par IBM qui a implémenté l' architecture du jeu d'instructions POWER . Le POWER2 était le successeur du POWER1 , fait ses débuts en septembre 1993 dans les systèmes RS/6000 d' IBM . Lors de son introduction, le POWER2 était le microprocesseur le plus rapide, dépassant l' Alpha 21064 . Lorsque l'Alpha 21064A a été introduit en 1993, le POWER2 a perdu la tête et est devenu deuxième. IBM a affirmé que les performances pour un POWER2 à 62,5 MHz étaient de 73,3 SPECint92 et 134,6 SPECfp92.

Le compilateur open source GCC a supprimé la prise en charge de POWER1 (RIOS) et POWER2 (RIOS2) dans la version 4.5.

La description

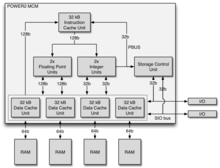

Les améliorations par rapport au POWER1 comprenaient des améliorations de l'architecture du jeu d'instructions POWER (composé de nouvelles instructions utilisateur et système et d'autres fonctionnalités liées au système), des fréquences d'horloge plus élevées (55 à 71,5 MHz), une unité à virgule fixe et une unité à virgule flottante supplémentaires , une plus grande Cache d'instructions de 32 Ko et un cache de données plus important de 128 ou 256 Ko. Le POWER2 était une conception multipuce composée de six ou huit circuits intégrés semi-personnalisés , selon la quantité de cache de données (la configuration de 256 Ko nécessitait huit puces). Le partitionnement de la conception était identique à celui du POWER1 : une puce d'unité de cache d'instructions, une puce d'unité à virgule fixe, une puce d'unité à virgule flottante, une puce d'unité de contrôle de stockage et deux ou quatre puces d'unité de cache de données.

La configuration à huit puces contient un total de 23 millions de transistors et une surface totale de puce de 1 215 mm 2 . Les puces sont fabriquées par IBM dans son processus CMOS de 0,72 m, qui présente une longueur de canal effective de 0,45 m ; et une couche de polysilicium et quatre couches d'interconnexion métallique. Les puces sont emballées dans un module multi-puces en céramique (MCM) qui mesure 64 mm sur 64 mm.

PUISSANCE2+

Une version améliorée du POWER2 optimisée pour le traitement des transactions a été introduite en mai 1994 sous le nom de POWER2+. Les charges de traitement des transactions ont bénéficié de l'ajout d'un cache L2 avec des capacités de 512 Ko, 1 Mo et 2 Mo. Ce cache a été implémenté hors package avec des SRAM en rafale standard de l'industrie. Le cache était connecté au POWER2+ via un bus 64 bits (pour les systèmes bas de gamme) ou 128 bits (pour les systèmes haut de gamme). Le cache était mappé directement , avait une taille de ligne de 128 octets et était accessible en écriture . Les étiquettes de cache étaient contenues sur la puce de l'unité de commande de stockage. Le POWER2+ dispose d'un bus mémoire 64 ou 128 bits plus étroit et d'un cache de données plus petit de 64 ou 128 Ko. Comme il y a moins de cache, les puces d'unité de cache de données sont par conséquent plus petites, et la puce d'unité de commande de stockage révisée est également plus petite. L'un des objectifs de la configuration à six puces était de réduire les coûts. Par conséquent, les puces sont emballées dans un boîtier à connexion par boule à souder (SBC) au lieu d'un MCM.

P2SC

Le P2SC, pour POWER2 Super Chip , est sorti en octobre 1996 en tant que successeur du POWER2. Il s'agissait d'une implémentation à puce unique du POWER2 à huit puces, intégrant 15 millions de transistors sur une puce de 335 mm 2 fabriquée selon le processus CMOS-6S métallique à cinq couches de 0,29 μm d'IBM. La première version fonctionnait à 120 ou 135 MHz, presque deux fois plus vite que le POWER2 à 71,5 MHz, avec la mémoire et les bus d'E/S fonctionnant à mi-vitesse pour prendre en charge la fréquence d'horloge plus élevée. IBM a affirmé que les performances de cette version étaient de 5,5 SPECint95_base et 14,5 SPECfp95_base. Une pièce 160 MHz plus rapide fabriquée dans le processus 0,25 m CMOS-6S2 a été annoncée au Microprocessor Forum en octobre 1997.

Le P2SC n'était pas une copie complète du POWER2, les capacités du cache de données L1 et du tampon de conversion de données (TLB) ont été réduites de moitié à 128 Ko et 256 entrées, respectivement, et une fonctionnalité rarement utilisée qui verrouillait les entrées dans le TLB n'a pas été implémentée dans afin d'adapter la conception originale sur une seule matrice.

Le P2SC a été remplacé par le POWER3 en tant que microprocesseur phare d'IBM sur la ligne RS/6000 en 1998. Une utilisation notable du P2SC était le supercalculateur IBM Deep Blue à 30 nœuds qui a battu le champion du monde Garry Kasparov aux échecs en 1997. les capacités de jeu d'échecs étaient dues à ses circuits intégrés personnalisés, plutôt qu'aux P2SC.

Voir également

Remarques

Les références

- Barreh, JI; Golla, RT ; Arimilli, LB; Jordan, PJ (septembre 1994). "Unité de cache d'instructions POWER2". Revue IBM de recherche et développement . 38 (5) : 537-544. doi : 10.1147/rd.385.0537 .

- Ball, Richard (15 octobre 1997). "Chipville États-Unis". Électronique hebdomadaire .

- DeTar, Jim (22 août 1994). "IBM détaille Power2+; DEC découvre le nouvel Alpha AXP". Nouvelles électroniques .

- Gwennap, Linley (4 octobre 1993). "IBM Regains Performance Lead avec Power2". Rapport du microprocesseur .

- Gwennap, Linley (26 août 1996). "IBM Crams POWER2 sur une seule puce". Rapport du microprocesseur .

- Hicks, Tennessee ; Fry, RE; Harvey, PE (septembre 1994). "Unité à virgule flottante POWER2 : Architecture et implémentation". Revue IBM de recherche et développement . 38 (5) : 525-536. doi : 10.1147/rd.385.0525 .

- Lineback, J. Robert (28 juin 1993). "IBM prépare RISC Progeny sous Unix" . Nouvelles électroniques .

- Shippy, David (9 août 1994). "Le processeur Power2+". Chips chaudes 6 .

- Shippy, DJ ; Griffith, TW (septembre 1994). « unités de contrôle de point fixe, de cache de données et de stockage POWER2 ». Revue IBM de recherche et développement . 38 (5) : 503-524. doi : 10.1147/rd.385.0503 .

- Statt, Paul (janvier 1994). "Power2 prend la tête--Pour l'instant". Octet .

- Blanc, SW ; Dhawan, S. (septembre 1994). "POWER2 : prochaine génération de la famille RISC System/6000". Revue IBM de recherche et développement . 38 (5) : 493-502. doi : 10.1147/rd.385.0493 .

Lectures complémentaires

- Weiss, Shlomo; Smith, James Edward (1994). PUISSANCE et PowerPC . Morgan Kaufmann. ISBN 1558602798. — Le chapitre 6 décrit l'architecture et le processeur POWER2